| |

|

|

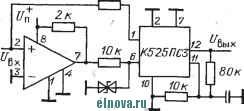

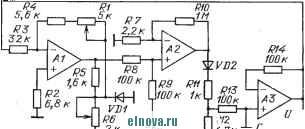

Главная » Книги и журналы 1 ... 10 11 12 13 14 15 16 ... 38 моугольных импульсов на 90°. Затем входные импульсы и сформированные на выходе А2 подаются на логический элемент A3, выполняющий функцию Исключающее ИЛИ. Интегратор и компаратор охвачены общей ОС, образованной цепью 2С2. С помощью этой цепи выделяется постоянная составляющая для задания режима работы А1, при котором выходное напряжение интегратора изменяется симметрично относительно нуля. Благодаря этому входные прямоугольные импульсы могут быть не обязательно симметричными относительно нуля. Диапазон рабочих частот схемы определяется выбором параметров R1, С1 и R2, С2. При заданных R1, С1 определен коэффициент передачи интегратора, который уменьшается при увеличении частоты. Следовательно, амплитуда выходного напряжения интегратора будет изменяться в зависимости и от частоты входного сигнала, и от его амплитуды. Чтобы с максимальной эффективностью управлять А2, размах выходного напряжения А1 должен быть больше 1 В. Другое ограничение на частотный диапазон обрабатываемых сигналов накладывается цепью R2C2. С одной стороны, при больших R2, С2 минимизируется влияние высокочастотных составляющих Ubx, с другой - .хуже отслеживаются быстрые изменения среднего уровня импульсов Ubx- Из сказанного выше следует, что оптимальным является соотношение RiCi 10 R\C\. Для устранения исходной ошибки на вы.ходе А2 можно через резистор R3 подключить к инвертирующему в.ходу Al источник регулирующего напряжения Lp. Соп- р^отивление R3 рассчитывается из выражения /?з~ - URx/Ubx, где Ubx - среднее значение входного напряжения. Схема утроения частоты значительно сложнее рассмотренных, поскольку для ее реализации необходимо выполнить две операции над входным сигналом. Сначала возвести синусоидальный входной сигнал Ubx В куб, а затем вычесть из утроенного входного сигнала значение 4 Lsinco Для возведения в куб используются два перемножителя. Первый с объединенными в.ходами дает на выходе t/ sina)/.. На входы второго перемножителя подаются значения Lsinco/ и Lsinco/ и на вы.ходе получается Ulsmatt. Затем в.ход-ной синусоидальный сигнал [/ sin и значение Ut sinw подаются на вход схемы вычитания на ОУ с требуемыми постоянными коэффициентами передачи и достигается утроение частоты, поскольку sin 3cL)/ = 3sinco/ -4sin(ti/. Амплитудный модулятор. Модулируемое по амплитуде колебание обычно описывается выражением Locos со(1f/racos <о/), в котором Locos cof - колебание несущей частоты, /( - коэффициент амплитудной модуляции, t/ cos сом/- модулирующее колебание. Поскольку произведение косинусов двух величин равно сумме косинусов разности и суммы этих величин, то из этого следует, что модулированное по амплитуде колебание состоит из трех составляющих: колебания несущей частоты и двух дополнительных колебаний с частотами сй + со и со -ш„. Коэффициент амплитудной модуляции оп- ределяет амплитуду колебаний с дополнительными - боковыми - частотами. При изменении /См в диапазоне от О до 1 амплитуда колебаний с боковыми частотами изменяется от О до Lo/2. Самым простым является амплитудный модулятор на базе К525ПСЗ (см. рис. 3.14). Глубину модуляции в этой схеме можно отрегулировать с помощью внешнего резистора за счет добавления к модулирующему сигналу части потенциала источника положительного напряжения питания. Поэтому в схеме можно получить полную модуляцию, т. е. Км=1 при Lo-0. Демодулятор. Чтобы выделить огибающую модулированного по амплитуде сигнала, достаточно умножить модулированный сигнал на усиленный сигнал несущей частоты (рис. 4.39). В этой схеме модулированный сигнал поступает на перемножитель К525ПСЗ и на компаратор К521САЗ. На стабилитроне формируется прямоугольное напряжение амплитудой от О до Lct. Величина Lct выбирается с таким расчетом, чтобы произведение Ua и максимальной амплитуды модулированного сигнала было меньше максимального размаха выходного напряжения перемножителя. В этом случае на выходе перемножителя появится выделенная огибающая модулированного по амплитуде в.ходного сигнала, содержащая короткие по времени выбросы в моменты перехода входного сигнала через нуль. Для устранения этих высокочастотных выбросов к выходу перемножителя можно подключить фильтр нижних частот (см. § 4,2), характеристическая частота которого приблизительно равна максимальной составляющей частоты огибающей модулированного сигнала. Работу демодулятора этого типа можно описать, используя обычные в этом случае математические соотношения для радиотехнических систем [14]. Немодулированные колебания прямоугольной формы с частотой несущей, которые сформированы на вы.ходе ком- паратора, можно записать в следующем виде: Uy{t)={4Uyo/n) X X[cos(2n -1)со/]/(2п-1). Поскольку модулированный по амплитуде сигнал обычно представляют в виде Ux{t)= Uocos Ш{1 -\-KmUmX X cos сОмО, выражение для выходного сигнала перемножителя UBb,x{t) = KuUx{t)Uy{t) можно упростить, учитывая только первые члены ряда для Uy{t), т. е. Usb,x{t)={4KnUxoUyo/n)[0,5{ + KmUX Xcos сОмО (1+cos 2cl)0 + (cos 2cl)/ + cos 4со)/2]. Пропустив получен-iOff  K521CAS 200 пФ Рис. 4.39. Схема демодулятора ный сигнал через фильтр нижних частот, получим Увых(0= = 2K UxoUyo{\+K.UK cos <Dj)/n. Фазовый детектор. Это устройство предназначено для преобразования в напряжение значения разности фаз двух сигналов Ui, и2- Обычно для двух сигналов фиксируются моменты перехода их через нуль, сравниваются, и разница по времени переходов через нуль преобразуется в напряжение. Построенный по такому принципу фазовый детектор (рис. 4.40) работает с сигналами произвольной формы. Два ОУ на в.ходе работают в режиме компараторов, сравнивающих текущие значения напряжения периодических входных сигналов с нулем. ОУ подключены к логическому элементу D1, выполняющему логическую операцию И (обведен штри.ховой линией). На базе A3 реализован фильтр нижних частот. Вы.ходное напряжение D1 изменяется от О до Lct- Напряжение и„ устанавливается на выходе D1, когда закрыты оба диода VD1, VD2. Эти диоды закрываются положительным напряжением на катодах. Если любой из диодов VD1, VD2 открыт, т. е. на один из катодов подано напряжение f/<;0 или Ue<CO, то транзистор закрыт и 6вых = 0. Если и совпадают по фазе, то напряжение на вы.ходе D1 равно половине периода изменения Ll, U2 и, следовательно, Ubux--VctR2/2Ri. Если Ui и U2 всегда изменяются в противофазе, то всегда U, UgD и 6вых = 0. С увеличением продолжительности совпадения .Ll и U2 по фазе пропорционально увеличивается Ubux- Описанное устройство контролирует изменения фазы в диапазоне ЛФ = 0... 180°, следовательно, Lbhx можно представить следующим выражением: 6вых=-АФLct/?2(/?i-360°). Точность работы устройства в основном определяется стабильностью . напряжения Uct и максимальной скоростью нарастания выходного напряжения А1, А2. Для существенного повышения точности и диапазона рабочих частот схемы необ.ходимо в качестве А1, А2 использовать компараторы К521САЗ и ввести в D1 переключаемый генератор стабильного тока для питания стабилитрона. После этого точность детектора будет в значительной степени зависеть только от параметров выходного фильтра.  \S,1K\] S,iK

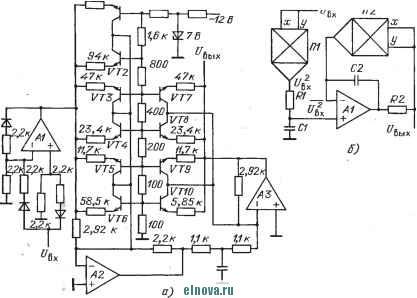

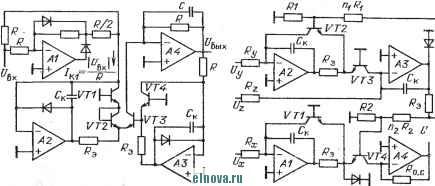

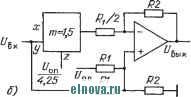

\VI]1 X 2S  £ых Рис. 4.40. Схема фазового детектора 4.7. ВЫПОЛНЕНИЕ СПЕЦИАЛЬНЫХ МАТЕМАТИЧЕСКИХ ОПЕРАЦИЙ Схема на рис. 4.41 обеспечивает извлечение квадратного корня с точностью 1% для входных напряжений, изменяющихся в диапазоне 0...100 В. Схема состоит из трех каскадов: каскада возведения в квадрат на А1, компаратора на А2 и повторителя напряжения на A3. Устройство работает посредством сравнения входного напряжения со значением квадрата входного напряжения, которое поступает по цепи ОС. Когда эти напряжения равны, то выходное напряжение равно корню квадратному из входного. Схема может работать для положительных в.ходных сигналов произвольной амплитуды, если на в.ход напряжение подается через делитель, например для t/вх =100 В необходим делитель 1:10. Входное напряжение сравнивается с отрицательным выходным напряжением А1 с помощью А2, на базе которого построен неинвертирующий усилитель с коэффициентом усиления, равным H\a/Ri. Выходное напряжение А2, которое всегда положительно, подается через фильтр, построенный на VD2 R11 -R13 и С1, на в.ход A3. Фильтр устраняет отрицательные выбросы выходного напряжения А2, возможные при быстрых изменениях t/вх, и сглаживает высокочастотные составляющие выходного сигнала А2. Схема возведения в квадрат на базе А1 выполняет требуемую функцию благодаря включению в цепь ОС ОУ диода VD1. Требуемая точность работы схемы возведения в квадрат достигается путем настройки всего устройства в некоторых точках диапазона изменения t/вх с помощью подстроечных резисторов R1 и R6. Сначала при t/Bx=10 В подстройкой резистора R1 устанавливается t/Bbix=VlO- Затем t/вх уменьшается, в нескольких точках проверяется выполнение равенства t/вых =Vt/Bx, и если необходимо, то производится подстройка с помощью R6. После этого вновь при t/Bx=10 В с помощью R1 устанавливается 1!въа=[ и затем при t/вх < 10 В подстраивается t/вых с помощью R6. Обычно после этого достигается точность вычисления корня квадратного, равная 1%, но если этой точности недостаточно, то производится третий цикл  иг и^,7к -г X. ±0,047 Рис. 4.41. Схема извлечения квадратного корня подстройки. Диод VD1 необ.ходимо подобрать таким образом, чтобы при напряжении на нем 0,8 В его сопротивление было примерно равно 160 Ом. Вычисление среднеквадратического -значения. К характеристикам, описывающим сигнал, относятся его среднеквадратическое, амплитудное и среднее значения. Среднеквадратическое значение наиболее полно описывает сигнал, так как является показателем энергии, которую он несет и которая не зависит от формы сигнала. Например, некоторые методы температурных измерений основаны на преобразовании теплового изменения сигнала в приращение энергии и измерении последней. Используя средства аналоговой вычислительной техники, можно произвести математическую операцию получения среднеквадратического значения, либо определяя среднюю величину сигнала и затем соответствующее ей среднеквадратическое значение, либо сразу вычисляя последнее. Хотя применение первого метода ограничено для некоторых типов сигналов, он проще реализуется. Для получения средней величины сигнал выпрямляется схемой выделения абсолютной величины и затем фильтруется. Из полученной .таким образом средней величины определяется среднеквадратическое значение после умножения на некоторый коэффициент, зависящий от формы входного сигнала. Для определения коэффициента преобразования среднее значение данного сигнала сравнивается с его среднеквадратическим значением с помощью уравнения U = =={\/T)\v\t)dt=4[m\ I Например, для синусоиды среднеквадратическое значение равно кредней абсолютной величине, умноженной на коэффициент 1,1. Щля биполярного прямоугольного сигнала коэффициент равен 1. При известной форме сигнала коэффициент преобразования можно учесть введением усиления сигнала непосредственно в схеме выделения среднего значения. Чтобы полностью реализовать указанную выще последовательность математических операций и выделить, таким образом, среднеквадратическое значение сигнала произвольной формы, можно воспользоваться схемами, показанными на рис. 4.42,-а. Первая схема обеспечивает точность около 1%. Входной каскад на Л7 выполняет операцию выделения абсолютного значения сигнала. Следующий каскад обеспечивает квадратичное преобразование напряжения. Он выполнен на усилителе А2 и кусочно-линейном аппрок-симаторе на транзисторах VT1 - VT6. Пороги срабатывания ап-проксиматоров задаются делителями напряжения в базовых цепях транзисторов, а проводимости соответствующих ветвей аппрокси-матора определяются резисторами в цепях эмиттеров. Пороговые напряжения аппроксимации изменяются в геометрической прогрессии, что позволяет получить достаточно высокую точность в широком диапазоне изменения амплитуды при небольшом числе ветвей. 1,Sk Ik  100 mk Рис. 4.42. Схемы вычисления среднеквадрати-ческого значения сигнала на транзисторах (а) и перемножителях (б) Фильтр нижних частот, включающий конденсатор С, интегри рует сигнал, выделяя тем самым из него низкочастотную составляющую на фоне случайных высокочастотных помех. Обратноквад-ратический преобразователь, служащий для линеаризации передаточной характеристики схемы, как и квадратический, состоит из кусочно-линейного аппроксиматора VT7 - VTIO и усилителя A3. Аппроксиматор обратноквадратического преобразователя содержит меньшее число ветвей, так как амплитудный динамический диапазон сигнала после интегрирования уменьшается. Преобразователь обладает единичным коэффициентом передачи эффективного значения. Отношение масимально допустимой амплитуды на входе к эффективному значению не превышает 7. Фильтр нижних частот имеет частоту среза около 10 Гц, определяемую емкостью конденсатора С. Диапазон изменения входного напряжения лежит в пределах ± 1 В, а максимальная частота преобразования /вх<С10 кГц. Схема на перемножителях показана на рис. 4.42, б. Выходной сигнал возводится в квадрат перемножителем D1, а затем усредняется полосовым фильтром верхних частот на А1. Параметры фильтра определяются из требуемых значений выброса и длительности переходного процесса. Вы.ход фильтра соединяется со входом ОУ, у которого в цепи ОС включен перемножитель для построения схемы вычислений среднеквадратического значения. Для того чтобы напряжение между в.ходами ОУ было близко к нулю. его выходное напряжение должно быть такое, чтобы выходные напряжения перемножителя D2 и фильтра были равны. Благодаря тому, что перемножитель в цепи ОС также возводит сигнал в квадрат, на выходе ОУ появляется среднеквадратическое значение входного напряжения. Точность преобразования около 5% ограничивается ошибками перемножителей и усилителей, а диапазон входного напряжения лежит в пределах ±10 В. Простую схему вычисления среднеквадратического значения сигнала можно построить на базе счетверенного ОУ К1401УД2 (рис. 4.43). Схема состоит из четырех функциональных блоков: выделителя абсолютной величины сигнала на базе А1, логарифмического усилителя на А2, антилогарифмического усилителя на A3 и интегратора-сумматора на А4. Вьщеление абсолютной величины сигнала необ.ходимо по той причине, что логарифмический усилитель обрабатывает только положительные сигналы. Схема на А1 преобразует входное напряжение в ток /к1 = I f/exl ?, протекающий в коллекторной цепи транзистора VT1. На коллекторе этого транзистора напряжение поддерживается близким к нулю с помощью А2. В цепь ОС А2 включены два транзистора, чтобы получить удвоенный логарифм от тока / т. е. возвести в квадрат в.ходное напряжение. Затем выходное напряжение А2 поступает на антилогарифмический усилитель, а точнее на эмиттер транзистора VT3, включенного в цепь ОС A3. Если в качестве VT1 - VT4 использованы идентичные по параметрам транзисторы, то справедливо равенство f/gBi +э.вг = э.бз +э.б4, где f/asi-э.б4 - соответственно эмиттерно-базовые напряжения VTI - VT4. Тогда токи, протекающие через транзисторы, будут связаны соотношением кз=к1к2/к4, где /к1-/к4 - соответственно токи через транзисторы VT1 - VT4. Последнее равенство будет тем точнее, чем больше /г21э транзисторов и чем меньше входные токи ОУ коллекторных токов транзисторов. Поскольку через транзисторы VT1 и VT2 протекает одинаковый ток, равный /к, =/г = I f/gx I ?, то получим ипъ:х = 1к,зЯ==л101у. Диоды в цепях ОС А2 и A3 исключают обратное смещение эмиттерно-базовых переходов транзисторов напряжением, большим 0,7 В. Назначение и выбор сопротивления Яэ и емкости С,( рассмотрены при описании логарифмического усилителя на рис. 4.27, б. Возведение в произвольную степень. Принцип построения логарифмических умножителей может быть использован для выполнения более сложной операции - возведения в степень (рис. 4.44). Функция умножения реализуется цепью, которую часто называют многофункциональной [9]. Как и в предьщущих схемах логарифмических умножителей, эмиттерно-базовые напряжения логарифмирующих транзисторов в цепях ОС ОУ суммируются или вычитаются так, чтобы обеспечить требуемое изменение напряжения на эмиттерно-базовом переходе транзистора VT4 антилогарифмического усилителя А4. Однако в отличие от описанных выше схем 5 Зак. 1396 . 129  Рис. 4.43. Схема для прецизионного вычисления среднеквадратического значения сигнала бых Рис. 4.44. Схема универсального узла умножения и деления в рассматриваемой логарифмирование сигналов производится с некоторым коэффициентом усиления или ослабления в зависимости от соотношения резисторов в делителе R1R2. Благодаря действию делителя R1 n\R\ сигнал на выходе A3 представляет собой умноженную в П1 + 1 раз разность между эмиттерно-базовыми напряжениями [/э. б2 и f/g. Бз транзисторов VT2 и VT3. Поскольку эти эмиттерно-базовые напряжения являются логарифмами от значений в.ходных сигналов, их увеличение вызовет соответствующее увеличение значения антилогарифма результирующего сигнала на выходе А4. Аналогичным образом уменьшение напряжения в делителе R2n2R2 вызовет соответствующее изменение сигналов, поступающих с А2 и A3 на антилогарифмический усилитель А4. Ослабление сигнала, вызванное делителем R2, П2/?2, будет выражаться в уменьшении в П2-{-1 раз напряжения f/g. б1 эмиттерно-базового пере.хода транзистора VT1, действующего на антилогарифмический усилитель. Результирующее изменение напряжения t/g. б4 на эмиттерно-базовом пере.ходе транзистора VT4 определяется выражением f/g, б4= э. ei Ч-С^э. вг - э. бз) ( i + 1)/(п2+1). Каждое из напряжений б1 - э. в4 связано логарифмической зависимостью с токами ./ki-/к4. протекающими в коллекторных цепях транзисторов VT1 - VT4. Предполагая идентичными параметры транзисторов, что справедливо для интегральных транзисторов, расположенных на одном кристалле, получаем /к4==к1 (кг/ /кзГ, где т=(п, + 1)/(п2+1). Учитывая, что для входных цепей А1 - A3 справедливы равенства Ux - Ux/Rx, 1к2 - у/у и Iv2 = U2/Rz (предполагая входные токи ОУ пренебрежимо малыми по сравнению с /к1-/к4). получаем UBbix=iRo.c/Rx)Ux{RzUy/RyUz) - Последнее выражение при выполнении равенства Ro.c==Rx-Ry приводится к виду 6вых = - Ui{Uy/UzT- Полученное выражение подтверждает определение описанной схемы как многофункциональной. Действительно, схема на рис. 4.44 позволяет производить не только умножение и деление аналоговых величин, а также возведение в произвольную степень и извлечение корня. Возведение в степень достигается при П2=0 и П1>0 выбором соотношения сопротивлений резисторов в делителе R1. tiiRu Извлечение корня можно получить, установив П1 = 0 и П2>0, варьируя соотношение сопротивлений резисторов в делителе R2, 2/?2. Чтобы получить отрицательное значение т, достаточно поменять местами входы Uy и Uz. Точность работы схемы определяется теми же факторами, что и в обычном логарифмическом умножителе. Дополнительное влияние оказывает точность отношения сопротивления резисторов делителей напряжений. Нелинейность вычислений обусловлена в первую очередь значениями сопротивлений эмиттеров транзисторов, а не согласованностью их параметров. Рассогласование параметров транзисторов приводит к ошибке смещения нуля и коэффициента передачи, как и в логарифмическом усилителе. В практической с^еме устройства трудно получить высокую точность за пределами диапазона т = 0,2 ... 5. Частотные свойства схемы зависят от амплитуды входных сигналов и значений R и С^. При малых амплитудах входных сигналов (менее 1 В) достаточно быстродействия ОУ типа К140УД7. При амплитудах входных сигналов более 1 В целесообразно использовать ОУ К154УДЗ или К154УД4 для получения минимальных динамических погрешностей. Диоды в схеме служат для защиты эмиттерно-базовых переходов транзисторов от действия обратных напряжений. Целесообразно использовать в качестве согласованных по параметрам транзисторов VT1 - VT4 транзисторную сборку К198НТ1. Реализация тригонометрических функций. В аналоговых и цифровых вычислительных машинах тригонометрические функции выполняют с помощью электронного устройства, реализующего вычисление линейной аппроксимации заданной функции. Требуемая передаточная функция устройства вычисляется в виде суперпозиции последовательности приращений линейных сегментов простейших функций от входного напряжения. Другими словами, вычисляется некоторый ряд величин, являющийся ближайшей аппроксимацией искомой функции. При таком вычислении точность расчета будет определяться числом сегментов аппроксимирующего ряда. Если достаточна точность вычислений около 1%, то реализовать тригонометрические функции можно сравнительно просто с помощью описанной выше многофункциональной схемы (рис. 4.44). Ниже рассматриваются примеры реализации функций синуса, косинуса и арктангенса. Синус числа может быть аппроксимирован рядом sinx=x-x / Ъ\-\-хуЪ\-х'р\+--- Реализовать функцию, записанную в правой части выражения, нетрудно с помощью перемножителей, делителей и одного ОУ для выполнения суммирования и вычисления сег- ментов записанного выше выражения для sinx. Но число требуемых для этого аналоговых микросхем будет чрезмерно велико даже при записанном числе сегментов ряда. Существенно меньшие аппаратурные затраты требуются при расчете синуса с помощью многофункциональной схемы (рис. 4.44). В приведенной схеме достигается точность вычисления около 0,2% и требуется дополнительно, к устройству возведения в степень лишь ДУ на одном ОУ. Выполняемая устройством на рис. 4.45, а математическая операция описывается при 0<; Ь'вх<;я6оп/2 следующим выражением: 6вых = -= (t/Bx-[/okV6,28t/i;f)/?2 ?i=(/?2t/on ?,)sin(t/Bx/t/on), где отношение Usx/Uon представляет собой угол, измеряемый в радианах. Значение Uon выбирается в зависимости от амплитуды входного напряжения с таким расчетом, чтобы максимальное значение Usr. не превышало 3,14 Uon- Изменение выходного напряжения можно регулировать выбором отношения R2/R1- Указанная выше точность выполнения функции синуса сохраняется только в пределах первого углового квадранта, т. е. при вычислении синуса угла, изменяющегося от О до 90°. Наибольшая точность вычисления достигается при исключении ошибок, обусловленных устройством возведения в степень и ДУ. Схема устройства, обеспечивающего вычисление косинуса угла с точностью около 1%, приведена на рис. 4.45, б. Устройство также состоит из многофункциональной схемы (см. рис. 4.44) и ДУ. Выполняемая математическая операция в данном случае имеет вид UBb,. = {Uon+UBx~6,08UJ/Uoh) R2/Ri={UonR2/Ri)cos (4,25 Увх/ Uon)- Выражение справедливо при изменении входного сигнала в диапазоне 0<6вх<я6оп/8,5. Как и в предыдущем случае, Uon выбирается исходя из максимального значения Увх, изменение выходного сигнала регулируется выбором отношения R2/RU а косинус вычисляется для изменения угла в первом квадранте. Чтобы вычислить тангенс угла, т. е. отношение синуса угла к косинусу, можно воспользоваться делителем, на входы которого поданы выходные напряжения, получаемые с выходов схем на рис. 4.45, а и б. Проще оказывается реализовать функцию арктангенса. Для этого необходимо включить ДУ в цепь ОС многофунк- 6х Won R1  Вых  Рис. 4.45. Схемы для вычисления синуса (а) и косинуса (б) угла 1 ... 10 11 12 13 14 15 16 ... 38 |